I am looking for silicon 6” in size Have a NOTCH instead a ![]() regular wafer flat (see details below) Clean for CMOS fab cleaning room operations. Si substrate preferred but don’t have to. Other layers on wafers probably don’t matter so long as they are compatible to CMOS fab. The quantity is likely 10 wafers or more. To be specific, the notch size that I am looking for is as the following. I guess its dimension is very likely a standard but need your expertise to judge. The reason I am buying Si wafers with notch is because I plan to use them as alternative wafers of SiC wafers in flat cut process development. Due to the expensiveness of SiC wafers, I use these test wafers as cheap alternative ones for initial wafer cutting test.

regular wafer flat (see details below) Clean for CMOS fab cleaning room operations. Si substrate preferred but don’t have to. Other layers on wafers probably don’t matter so long as they are compatible to CMOS fab. The quantity is likely 10 wafers or more. To be specific, the notch size that I am looking for is as the following. I guess its dimension is very likely a standard but need your expertise to judge. The reason I am buying Si wafers with notch is because I plan to use them as alternative wafers of SiC wafers in flat cut process development. Due to the expensiveness of SiC wafers, I use these test wafers as cheap alternative ones for initial wafer cutting test.

Silicon Wafer for CMOS Research

A scientist was in need of silicon wafers:

UniversityWafer, Inc Quoted:

Silicon Wafer

6", 650um, SSP, P<100>, 1-100 ohm-cm

Quantity: 10 Wafers

FOB Price: $Contact us for pricing

Get Your Quote FAST! Or, Buy Online and Start Researching Today!

Sapphire Wafers for CMOS Research

A materials scientist requested help with their questions:

There is some interest in the 150mm Sapphire Subsstrate r which you quoted last month. Are you able to specify / measure/ guarantee surface or bulk metals on sapphire wafers to a specification of <3E10 atoms/cm2 for the following heavy metals: Al, Cr, Cu, Ca, Fe, K, Ni, Na, Zn.

Do you have a cleaning process in place for heavy metal element control on the wafer surface?

Our customer would like to use the wafer in a CMOS compatible environment which requires contamination control of heavy metals. Do you have any more information regarding impurities in the bulk beyond the 99.996% purity specification?

Answer:

1. Are you able to specify I measure/ guarantee surface or bulk metals on sapphire wafers to a specification of <3E 10atoms/cm2 for the following heavy metals: Al, Cr, Cu, Ca, Fe, K, Ni, Na, Zn.

Rep: Actually,we do have the GDMS test report , like attached pic_‘GDMS test report“

But , regarding for the Metallic Contamination ,we do not have the tesgt date .

1stly ,we have contact the tester to check the 6 inch size of wafers by send the samples to American , will test by ICP-MS or VPD and the reference result will be get feedback several weeks manybe longer . We will feedback you the more details as soon as we get the test result .

2ndly ,maybe we also could send samples to your side to test/ check and could compare the test dates .

2. Do you have a cleaning process in place for heavy metal element control on the wafer surface?

Rep: Yes ,we do have the cleaning process to control the heavy metal element ,such as we use the H2SO4 / H2O2/semi-conduct purity wafer to cleaning the wafers ,We also control the heavy metal element by control the medicine /water .

Unlike Silicon, sapphire itself is less prone to metal ion adsorption.

3. Our customer would like to use the wafer in a CMOS compatible environment which requires contamination control of heavy metals. Do you have any more information regarding impurities in thebulk beyond the 99. 996% purity specification?

Rep: we have a GDMS / MSDS /ROHS test report for your reference ...Hope will be useful .. if you have any further question ,please feedback to me.

How do high-frequency CMOS chips manage heat dissipation from switching power loss?

High-frequency CMOS chips inevitably generate heat due to their dynamic (switching) power losses, which scale with frequency. Managing that heat is critical for reliable performance. Below is an overview of the most common techniques and design strategies used to handle switching power dissipation and the resulting thermal challenges:

1. Reducing Power at the Device and Circuit Level

a. Lower Supply Voltage

- Dynamic power is proportional to V2V^2. Dropping the supply voltage (VDD) is one of the most direct ways to curb switching power.

- This approach is central to modern process nodes, where nominal VDD has steadily decreased (e.g., from 5 V in older CMOS to below 1 V in advanced FinFET/FD-SOI nodes).

b. Minimizing Load Capacitance

- Dynamic power is also proportional to the load capacitance CC.

- Designers minimize parasitic capacitances through careful layout, using smaller transistors, shorter interconnects, and advanced device structures (e.g., FinFETs, GAA-FETs).

- Techniques like layout optimization and gate sizing further ensure minimal switching capacitance.

c. Reducing Switching Activity

- Power also scales with the switching activity factor α\alpha. Not all gates switch on every clock cycle.

- Clock gating and power gating selectively shut off clock signals or entire circuit blocks when they are idle, significantly reducing dynamic power.

- Data gating or operand isolation can similarly reduce unnecessary toggling of internal signals.

2. Architectural and System-Level Techniques

a. Parallelism and Multi-Core Architectures

- Instead of pushing one core to extremely high clock frequencies, modern designs use multi-core architectures running at moderate frequencies.

- This approach spreads out workload (and heat generation) while avoiding the exponential increase in power associated with very high frequencies in a single core.

b. Dynamic Voltage and Frequency Scaling (DVFS)

- Systems monitor workload and temperature to dynamically adjust clock frequencies and supply voltages on the fly.

- When high performance is needed, voltage and frequency go up; during idle or light load, they go down—managing both power and heat.

c. Thermal-Aware Floorplanning

- During the physical design (place-and-route) stage, high-power blocks are distributed to reduce localized hotspots and improve overall heat spreading.

- Critical analog, memory, or other blocks might be placed strategically for better thermal management (e.g., near heat sinks or away from other hot blocks).

3. Packaging and Cooling Solutions

a. Advanced Packaging

- Flip-chip ball grid array (FC-BGA) packages place the silicon die face-down onto the package substrate, which shortens interconnect lengths and provides better thermal conduction paths.

- 3D stacking (through-silicon vias, TSVs) includes careful thermal considerations because stacking can concentrate heat in small volumes.

b. Heat Spreaders, Heat Sinks, and TIM

- Integrated heat spreaders (IHS) on top of the die help conduct heat to larger external surfaces.

- Thermal interface materials (TIMs) (greases, gels, phase-change materials) improve conduction from the chip to external heat sinks or cold plates.

c. Active Cooling Systems

- High-performance systems often rely on fans, vapor chambers, or liquid cooling to extract heat from the CPU/GPU package.

- Data centers may use immersion cooling or specialized chilled-water cooling loops for extremely dense compute solutions.

4. Advanced Transistor and Process Technologies

a. FinFETs and GAA (Gate-All-Around)

- These 3D transistor structures improve electrostatic control, lowering both leakage current and some parasitics, which in turn reduces the overall power.

- Better subthreshold swing helps keep supply voltages lower while maintaining performance, thus reducing both dynamic and static power.

b. FD-SOI (Fully Depleted Silicon-On-Insulator)

- The thin oxide layer in SOI processes reduces parasitic junction capacitances, lowering dynamic switching losses.

- Designers can also apply back-bias to adjust transistor thresholds dynamically, balancing performance and power.

5. On-Chip Power Distribution and Regulation

- On-die voltage regulators (e.g., low-dropout regulators or switching regulators) can provide fine-grained voltage domains.

- Smaller, localized power domains help regulate supply precisely, minimizing both IR drops and unnecessary power consumption.

6. Design Tools and Methodologies

a. Power Analysis and Profiling

- Electronic design automation (EDA) tools perform static and dynamic IR drop analysis and thermal simulations.

- Early in design, power analysis tools predict hotspots and guide design decisions (e.g., block placement, timing constraints).

b. Power-Aware Synthesis

- Synthesis tools optimize logic at the gate level with power-specific objectives, balancing timing closure and minimal switching power.

Putting It All Together

- Reduce the causes of switching power: Lower the supply voltage and minimize parasitic capacitances.

- Control switching activity: Employ clock/power gating and advanced architectural techniques (e.g., multi-core, DVFS).

- Enhance heat extraction: Use advanced packaging, heat spreaders, and, if necessary, active cooling solutions.

- Optimize transistor technology: Transition to FinFETs, GAA-FETs, or FD-SOI to reduce both dynamic and leakage components.

- Design for thermal awareness: Floorplanning and EDA-driven optimization ensure that local hotspots are minimized.

These strategies collectively allow modern high-frequency CMOS chips to manage heat dissipation from switching power losses, enabling the ever-increasing performance demands of today’s semiconductor industry.

Is It Difficult to Beat Silicon for Complementary Metal Oxide Semiconductors?

CMOS (Complementary Metal Oxide Semiconductor) is a technology that uses two different combinations of metals in the construction of integrated circuits. It is used in transistors in computer microchips, and is increasingly important in applications such as automotive and image sensors. It is expected that the use of CMOS will increase significantly with the increasing popularity of smartphones. Regardless of its benefits, it remains difficult to beat silicon when it comes to performance.

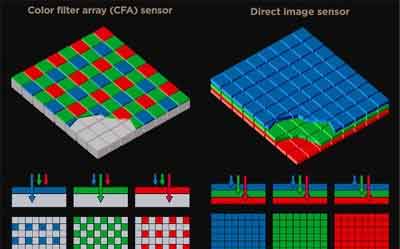

A typical complementary metal oxide semiconductor (CMOS) has an electronic rolling shutter design. In this  design, data is not passed from one bucket to another, but rather is read from one bucket to the next. The CMOS sensor implements an electronic rolling slit shutter by causing a reset on each row. This process limits the speed at which the wave passes over the sensor. In order to make all rows of CMOS devices equally exposed, the waves must precede each other.

design, data is not passed from one bucket to another, but rather is read from one bucket to the next. The CMOS sensor implements an electronic rolling slit shutter by causing a reset on each row. This process limits the speed at which the wave passes over the sensor. In order to make all rows of CMOS devices equally exposed, the waves must precede each other.

Despite the success of CMOS, the technology is facing fundamental scaling limitations. While Moore's law pushed down the cost of integrated circuits, it also caused a rise in power consumption. To overcome this scaling problem, new strategies are needed. These include the "More than Moore" and "Beyond CMOS" strategies. The resulting product is more efficient and has lower power consumption than the competition.

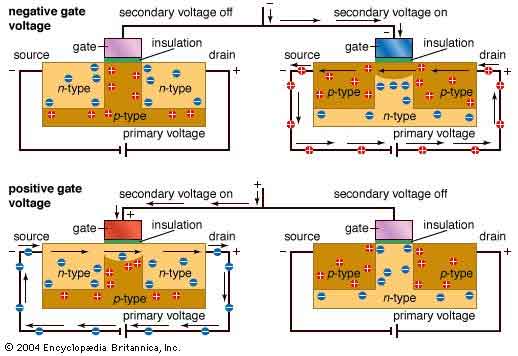

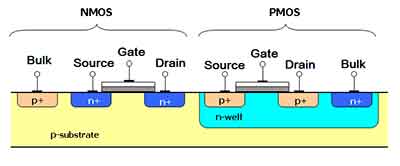

CMOS-MOS technology combines a p-type and n-type metal oxide semiconductor to produce an integrated circuit. This design technology is commonly used for RF and digital logic circuits. It is also used for image sensors, data converters, and highly integrated transceivers. The advantages of this semiconductor technology are numerous and many. However, the downside is that it is difficult to scale, making it a challenging and expensive option.

A complementary metal oxide semiconductor (CMOS) is a semiconductor that has complementary symmetry. It is a type of MOSFET that uses a complementary pair of p-type and n-n-n junctions to form the transistor. It is widely used in digital logic circuits, and is an ideal choice for mobile devices and cameras. Its high-performance capabilities make it an ideal material for a variety of applications.

CMOS technology has been the standard for decades. Unfortunately, it is nearing its limits, and other semiconductors will need to find innovative solutions to this challenge. In addition to the intrinsic strengths of silicon, CMOS-based semiconductors are also cheaper and more efficient. The current generation of CMOS chips is expected to surpass the performance of the III-V semiconductors in the next few decades. They can be fabricated in larger quantities, and can be etched into smaller areas.

Complimentary metal oxide semiconductor (CMOS) technology is the basic logic controller of integrated circuits. Its high integration and low power consumption makes it the preferred material for a wide variety of applications. The CMOS technology is also a great choice for a number of other applications, such as image sensors and CMOS image sensors. The CMOS technologies are becoming the standard in smartphones, but they are still limited by their power limitations.

CMOS-based silicon technology is facing fundamental scaling limitations. While the Moore's law has enabled high integration and performance without reducing power consumption, this trend has led to a steep decline in the power of the devices. As a result, new strategies are needed for the semiconductor industry to continue to grow. Several emerging CMOS technologies are being developed to address these challenges. The first generation of CMOS uses copper, while a complementary metal oxide semiconductor uses an iron-based alloy.

In terms of power consumption, the complementary metal oxide semiconductor (CMOS) is a type of semiconductor with low power consumption. This technology is used for analog and digital ICs and is gaining popularity with smartphones and mobile devices. Because of its low power consumption, it is also used in other applications, including wireless communications and memory. The technology is gaining more popularity in consumer electronics. These devices are becoming increasingly useful and popular as everyday products.

What are some possible materials to replace CMOS after graphene and carbon nanotubes?

In the quest to replace CMOS (Complementary Metal-Oxide-Semiconductor) technology for building more efficient and powerful electronic devices, researchers have been investigating a wide variety of materials other than graphene and carbon nanotubes. Here are some materials and technologies that are considered potential successors to CMOS:

1. New Semiconductor Materials

-

2D Materials Other Than Graphene: This includes materials like molybdenum disulfide (MoS₂) and tungsten diselenide (WSe₂), which have shown potential in transistor applications.

-

Black Phosphorus: This material has been found to have excellent electronic properties and has been researched for its use in transistors.

-

Silicene: It is a two-dimensional allotrope of silicon and has properties similar to graphene.

-

Germanene: Similar to silicene, this is a two-dimensional allotrope of germanium.

2. Spintronics

-

Topological Insulators: These materials behave as insulators in their interior but support conducting states on their surface, offering new possibilities for transistor design.

-

Magnetic Materials: Materials that leverage electron spin rather than charge can be used in spintronic devices.

3. Quantum Materials

- High-Temperature Superconductors: These materials can conduct electricity without resistance at relatively high temperatures, promising energy-efficient technologies.

4. Emerging Computing Paradigms

-

Phase-Change Materials: These materials can change their physical properties based on external conditions, opening up avenues for novel memory and computing technologies.

-

Memristors: These are two-terminal non-volatile memory devices that store and process information similarly to the way synapses work in biological systems.

5. Quantum Computing

-

Superconducting Qubits: Materials such as Josephson junctions, which are made from superconductors, are used in quantum computers.

-

Topological Qubits: These rely on particles called anyons, which are theoretically predicted to be extremely useful for stable quantum computing.

6. Organic Semiconductors

- Organic Molecules: There has been research into using specially designed organic molecules to create semiconductors.

7. Nanomaterials

-

Quantum Dots: Nanoscale semiconductor particles that have quantum mechanical properties.

-

Nanowires: These have potential applications in nanoscale transistors.

8. Perovskite Materials

- Halide Perovskites: These materials are being researched for a variety of applications including photovoltaics and light-emitting diodes (LEDs), and could potentially find uses in semiconductor devices.

Conclusion

While all of these materials and technologies hold promise, it is worth noting that they are largely in the research and development stage, and significant breakthroughs will be needed to make them viable replacements for current CMOS technology. It will be a combination of material discovery, technological innovation, and industry adaptation that will dictate the next leap in computing technology.

electrical components are called 'bits'. The CMOS style is used in constructing computers and is governed by a set of rules that writers should follow. When writing about CMOS, the word 'CMOS' refers to a chip that is made of a combination of several transistors.

electrical components are called 'bits'. The CMOS style is used in constructing computers and is governed by a set of rules that writers should follow. When writing about CMOS, the word 'CMOS' refers to a chip that is made of a combination of several transistors. CMOS chip is a semiconductor chip that contains a number of different circuits. Its main function is to set up the computer, load the drivers, and boot the operating system. CMOS is also used to configure BIOS settings, which is why it is crucial to understand how these devices work.

CMOS chip is a semiconductor chip that contains a number of different circuits. Its main function is to set up the computer, load the drivers, and boot the operating system. CMOS is also used to configure BIOS settings, which is why it is crucial to understand how these devices work. photoelectric signals, which are then sent to the analog-to-digital conversion circuits, located adjacent to the photosensitive region. In addition to generating voltage, a CMOS image sensor also has many other duties. It is used in video cameras to store digital images. However, it must be understood that a CMOS image-sensor pixel has a lot more complexities than it appears at first glance.

photoelectric signals, which are then sent to the analog-to-digital conversion circuits, located adjacent to the photosensitive region. In addition to generating voltage, a CMOS image sensor also has many other duties. It is used in video cameras to store digital images. However, it must be understood that a CMOS image-sensor pixel has a lot more complexities than it appears at first glance. manufactured on silicon wafers. These semiconductor wafers are also known as CMOS monolithic pixel sensors. There are two types of CMOS substrates. The first one is called an epitaxial wafer and the other one is referred to as a non-epitaxial high resistivity type.

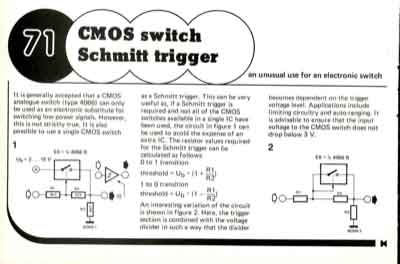

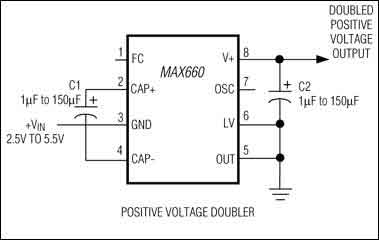

manufactured on silicon wafers. These semiconductor wafers are also known as CMOS monolithic pixel sensors. There are two types of CMOS substrates. The first one is called an epitaxial wafer and the other one is referred to as a non-epitaxial high resistivity type. supply voltage is desired when a system has ground-referenced signals and digital logic. While this requirement is relatively low, a negative supply voltage can be extremely expensive and inefficient. This circuit converts the positive and negative supply voltages using only two non-critical capacitors. If the input voltage is higher than 6.5V, a diode is added to protect the device.

supply voltage is desired when a system has ground-referenced signals and digital logic. While this requirement is relatively low, a negative supply voltage can be extremely expensive and inefficient. This circuit converts the positive and negative supply voltages using only two non-critical capacitors. If the input voltage is higher than 6.5V, a diode is added to protect the device.