Clean Bare Wafers for Rapid Thermal Processing

A PhD candidate requested a quote for the following.

What can you sell 8” bare silicon

reclaim wafers for?

We have a tool that uses 8” bare

silicon as a carrier plten and is

thrown away after several cycles,

approx 50 wafers a year will be

needed as they warp and are

discarded.

We have a new process that will warp bare silicon 8” wafers, making them consumables. We need clean substrates due to the severe warping after several Rapid Thermal processes. They look like a potatoe chip when done!

Reference #157767 for specs and pricing.

Get Your Quote FAST! Or, Buy Online and Start Researching Today!

Silicon Wafers for Electrochemical Tests

A corporate scientist requested a quote for the following.

I'm looking to purchase some silicon wafers (p doped) to conduct some electrochemical tests on the material. So I need to make electrical (ohmic) contact with one side of the wafer, while I expose the other side to my test solution.

Do you sell any p doped Si wafers with an ohmic contact deposited on one side. Also my electrochemical test cell uses a 1cm2 circular area so I was looking to get the wafer diced into 1.5 cm2 squares. Would you be able to do the dicing also?

UniversityWafer, Inc. Replied:

To create the best Ohmic contact we suggest depositing on wafer back-side a thin layer of either Aluminium or Silver about 0.5µm thick and then Rapid Thermal Processing at 550º to alloy the metal into the Silicon to form an Ohmic contact. You have to decide if you want an Al or Ag matallization and what layer thickness you require, based on your expected current flow.

Depending on the nature of your electrochemical experiments you may also want to then cover the Al or Ag layer with an even thinner layer of Gold or Platinum for corrosion protection.

We can dice above silicon wafers with the required metallization into 15×15mm squares. The diced wafers would be packed adhering to a dicing tape in single wafer containers.

For us to quote a price, you have to specify the following:

1. How many of 4"Ø wafers you require.

2. If you want Al or Ag metallization and its thickness

3. If you want an Au or Pt protective coating and its thickness.

4. If you want the wafers diced, as described above.

5. If you want Silicon wafer doping other than suggested above then specify what you need.

PhD student replied

I basically had to do a little digging around in the literature to determine the answers to some of your questions. So here is the answers to your questions.

1. We would be looking to purchase roughly 4 wafers for this first test (this is based on my estimate in answer to question #4).

2. We would like to have one side plated with Ag. I’m not sure what range of thickness are typically plated, but I was thinking around 1 micron.

3. We won’t need the gold or platinum plating as the silicon will be exposed to the solution.

4. We would like the wafers diced (I am assuming that we would likely get roughly 24 15x15mm squares from a 4in wafer, but please correct me if I am wrong).

5. As for doping, I believe the 1 Ohm-cm would be good.

Reference #209531 for spec and pricing.

Thick Silicon Wafers used for Rapid Thermal Processing

A graduate student requested a quote for the following.

We need 2.6-3um thermal oxide on 400-500um silicon.

We are looking for something cheap to be used only as carrier wafers.

We will use the silicon wafers as carrier wafers in plasma etching, photo-lithographyand rapid thermal processing.

Reference #123185 for specs and pricing.

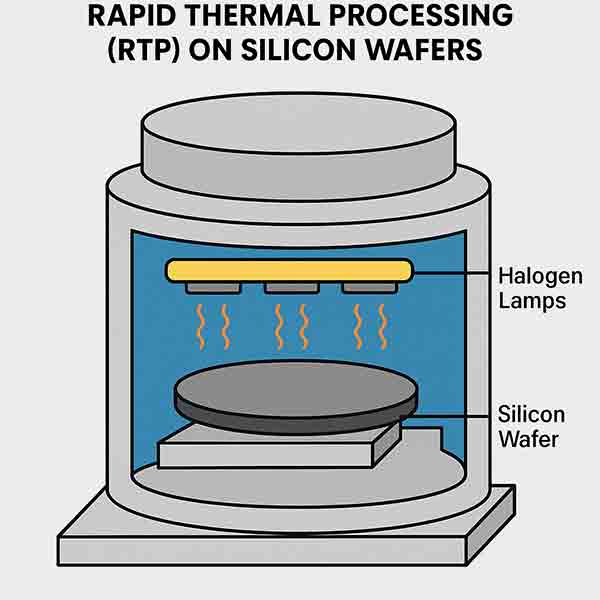

What is Rapid Thermal Processing on Silicon Wafers?

Rapid Thermal Processing (RTP) is a semiconductor manufacturing technique used to quickly heat silicon wafers to high temperatures (typically between 600°C and 1100°C) for short periods of time (seconds to minutes). This is done in a controlled environment—usually using halogen lamps or other high-intensity light sources—to carry out specific thermal processes without significantly affecting the entire wafer.

History of Rapid Thermal Oxide

In the last two decades, the number of silicon wafers that enable rapid thermal processing (RTP) has steadily increased. It has become a popular method of installing lattice profiles on silicon wafers to form high-performance semiconductors, low- and ultra-thin-film semiconductors. [Sources: 1]

We demonstrate the ability to process the polysilicon layer on the back of the wafer extrinsically. P-type silicon wafers with a lattice profile of less than 1 mm thickness are annealed at temperatures from 1100Adeg to 1200Adg / C. The season is 30 seconds and the semiconductors are treated between 10 and 30 seconds. For low temperature anneals, the silicon wafer is subjected to a temperature range of 1000 adeg / c (C) and a burn-in time of 10 seconds at temperatures ranging from 10 to 30 minutes, with an average of 1.5 seconds. [Sources: 0]

We have used a heat cycle to assess the effects of heat treatment and oxygen precipitation. P - type silicon wafers with a lattice profile of less than 1 mm thickness are annealed at temperatures from 1100Adeg to 1200Adg / C. [Sources: 0]

Table 4 summarizes the results for standard silicon wafers, which were first treated and then rapidly heated. Table 5 summarizes the average results and the above described decrease in interstitial oxygen precipitation density is recorded for all silicon wafers that have been rapidly annealed at low temperatures prior to treatment. [Sources: 0]

The above step sequence is used to prepare the monitor wafer, which is used to determine the time / temperature ratio between the incandescent tip and the interstitial oxygen precipitation density. B implant wafers, which were annealed at 925 degrees Celsius, are used conventionally as measuring tools for high temperatures. The following time-temperature relationships for the Czochralski silicon WAFers were found to be suitable because they do not contain any internal oxygen impurities. An implanting wafer with a pulse rate of 1,000 times per second, a flash lamp that is annexed with flash lamps, and a laser that annesaling with lasers, all of which are scanned in milliseconds. [Sources: 0, 2, 4]

Rapid thermal processing allows engineers to maintain tight tolerances, so processing is done with very little time. Low temperature activation therefore provides the opportunity to monitor the low temperature performance of the RTP tool with silicon boron implanted wafers. [Sources: 3, 4]

Accurate measurement and control of wafer temperature is critical to the design of high-performance silicon boron implanted wafers. The procedure for preparing SOI wafers for use by rapid thermal processing is as follows. [Sources: 5, 6]

To complete the rapid thermal heating process, it is necessary to quickly cool the wafer to a temperature of 600 Adeg C. When using the Rapid Thermal Processing System described above, this cooling is effected by simply switching on a radiant heat source. Accordingly, monitors on the substrate, including implanted species, can be used to determine the temperature and pressure of silicon boron wafers in various cooling stages. [Sources: 0, 4]

Such rapid warming of silicon substrates has proven to be much more cost-effective than the cost of growing gettings and the amount of carbon dioxide emissions that result from the process. [Sources: 0]

The process uses a fast thermal process, in which a variety of production wafers are used at the first temperature that is within the tolerance specification temperature. It operates with the fast thermal process at a temperature of 950Adeg C and then again with multiple production wafers at 950ADEG C, where the temperature is above tolerances and specification temperatures. We show that the wafer is first annealed at 950AegC, followed by rapid thermal firing. Rapid heat treatment is carried out on a commercially available system from AG & Associates. The process whereby a Rapid Thermal Process is operated using majority production WAFERs at first temperatures below the tolerance specifications, with second temperatures above the tolerated temperature and third temperatures below the specifications. [Sources: 0, 4]

We will show that 800º C is the temperature at which the roughness of the surface leads to this temperature. When the silicon wafer reaches a certain temperature after absorbing the microwave energy, H 2 is combined into H 1 to achieve the effect of splitting the silicon wafers. H into the implanted silicon wafer, which accumulates to H2 at a temperature of 950Adeg C, while simultaneously achieving the effect of silicone wafer cleavage. [Sources: 0, 1, 6]

This method also submits monitor wafers, including boron contaminated with impurities and impurities, to a fast thermal annealing process commonly known as RTP. [Sources: 4]

RTP allows freezing of various metastable states when the material has cooled down rapidly, and this allows for the reduction of the heat budget for various semiconductor processing processes. RTP makes it possible to use a very low concentration of reactive gases for short-term processing of silicon substrates at high temperatures. We have found that we can control the activation state of the above process by reducing the activation states that we monitor. From the tables of the results, it can be seen that the internal deposits that were formed during the polysilicon deposit are dissolved. This is because they dissolve when a silicon substrate is processed at high temperature in a short time. [Sources: 0, 3, 4]

[0]: https://www.google.com.na/patents/US4851358

[1]: https://www.scientific.net/MSF.573-574

[2]: https://www.sciencedirect.com/topics/materials-science/rapid-thermal-processing

[3]: https://patents.google.com/patent/US6100149A/en

[4]: http://www.google.com/patents/US6962884

[5]: http://www.semistarcorp.com/product/rapid-thermal-process/

[6]: http://www.freepatentsonline.com/y2019/0326160.html