How Is Thermal Oxide Leakage Measured?

Thermal Oxide Leakage Question

Scientists Question:

Q. Hows the leakage issue of the thermal oxides?

A. Wet thermal oxide isn’t really designed for insulation/isolation. It is great for photolithography masking, but is too porous to make a good insulator. At 300nm it may work if the conditions are not too extreme. Our recommendation for isolation oxides or gate oxides is Dry Thermal Oxide, especially Dry Thermal Chlorinated Oxide. 300nm of this should take care of leakage. There is the top of the line oxide, Dry Thermal Chlorinated Oxide with an anneal in forming gas, but this isn’t usually needed.

Summary – 300nm of wet oxide may be fine, but it is better to go with 300nm of dry oxide and maybe one of the upgrades.

We don’t have any data on leakage or breakdown voltage. This depends too much on the customer’s processing and on their test method.

Get Your Quote FAST!

Advantages and Disadvantages of Thermal Oxide

The thermal oxide is a semiconductor material deposited using a process that produces a thin layer of oxygen. It has excellent electrical properties compared with other semiconductors and can be used to generate a scalable high-voltage IC. Its dielectric constant (K) and density are stable over time and are comparable to those of silicon oxide. It also exhibits good thermal conductivity and thermal stability. Its leakage current is small compared to other materials in the same operating voltage range.

One of the main disadvantages of thermal oxide is that it is not designed for insulating applications. However,  it is excellent for photolithography masking. It may be effective at 300 nm if the conditions are right. Dry Thermal Chlorinated Oxide is a much better alternative. Unlike wet thermal oxide, it anneals in a gas, making it a much better insulator.

it is excellent for photolithography masking. It may be effective at 300 nm if the conditions are right. Dry Thermal Chlorinated Oxide is a much better alternative. Unlike wet thermal oxide, it anneals in a gas, making it a much better insulator.

The oxidation process produces two different oxide films, one with a low leakage current and one with a higher breakdown voltage. The first one is not very efficient at insulating, while the other is ideal for masking in photolithography. In the photolithography process, the wet thermal oxide is also a poor insulator. Besides, thermal chlorinated oxide is more effective in photolithography.

The other one is thermal oxide, which is used to protect photolithography devices. It has low leakage current and high breakdown voltage. This means that the wet type does not provide good insulation. On the other hand, the dry type can be a better option than wet thermal oxide. The Dry Thermal Chlorinated Oxide is also better than wet thermal oxide. During a photolithography process, the dry type does not have any defects in the photolithography masking.

A silicon containing film can be used as the gate insulator of a metal oxide layer. The deposition temperature must be between 400 and 500 degrees C. The thickness of the silicon containing film is very thin. It must have a conformality of at least 50% and a high leakage current density of 1x107 A/cm2. If the silicon nitride is too thin, the photolithography process will not be effective.

A silicon containing film can be used as the gate insulating layer for the metal oxide layer in a semiconductor device. It must have a deposition temperature of 400 degrees C. Its O/Si ratio should be between 1.9 and 2.0. Its deposition rate must be higher than this to be a better option. A silicon containing film can be more conductive than a dry film. Therefore, the wet thermal oxide should be used as a gate insulator for the semiconductor device.

Wet thermal oxide has a very low leakage current compared to dry thermal oxide. It is a good material for masking photolithography processes but is not suitable for insulating semiconductor devices. It can be deposited at high temperatures without the use of solvents. A silicon containing film is also used as gate insulator in display devices. For a high-quality conductive film, it must be able to resist a large amount of heat.

Wet thermal oxide has no insulation properties and is only good for photolithography masking. It is too porous and prone to leakage. The dry thermal chlorinated oxide is much more suitable for this application. It is a liquid that does not form gas. The silicon containing film is highly flammable and must be handled with care to avoid chemical reactions. It is possible to produce a silicon containing film with high-quality properties.

The deposition rate of wet thermal oxide depends on how the thermal oxide is processed. In general, 3ES deposited films have similar leakage current and break down voltage to thermal dioxide. A wet thermal oxide is not a good insulator and may be better used as a photolithography masking layer. In contrast, dry thermal chlorinated oxide has better insulating properties. The annealing in the forming gas makes it better than wet thermal chlorinated oxide.

Thermal oxidation is the most effective method of removing VOCs and odors from exhaust air. It is best suited for exhaust air streams that have low organic content. This technique is an effective way to get rid of VOCs and odors. And it is also an effective process for reducing heat transfer from a building. In addition, it is a safe method for producing high-quality semiconductors.

What is Thermal Oxide Leakage?

In microfabrication, thermal oxidation is one of the ways to produce powerful, cost-effective and environmentally friendly silicon wafers on the surface of a wafer. Improving the performance of tetraethylorthosilicate (TEOS), which is used as a silicon source, is a well-known technique for the precipitation of a large amount of thermal oxidizing agent (TOS) in the form of silicon oxide. [Sources: 2, 10]

The oxidant H 2 O penetrates into the thermal oxide layer [18], which is thermally cultivated by wet oxidation. The surface of the wafer is oxidized and forms a gate-oxide layer in which gate-oxide layers for integrated circuits are formed [19]. [Sources: 1, 6]

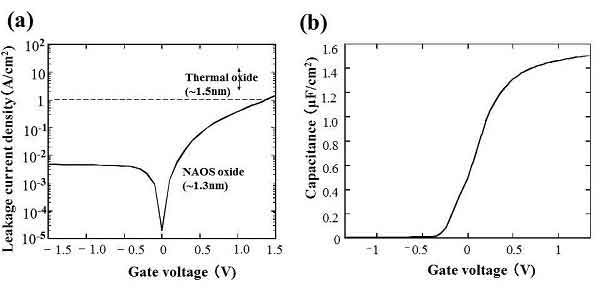

The surface of the semiconductor substrate must be extremely clean to reduce the oxide leakage current. The growth rate of the oxides is very fast, but slows down as oxygen diffuses through the silicon substrate before it reaches it. As soon as the EOT of the silicon oxide layer drops below about 20 angstroms, it becomes imperative to reduce the leakage current of the oxides [19]. [Sources: 0, 6, 11]

Furthermore, the skilled workers will appreciate that the rapid thermal oxidation process described above is exemplary and that various parameters for rapid thermal oxidation can be used to form the silicon oxide layer [42]. The chemical oxide layers protect the silicon surface from roughening after high-temperature oxidation and the final SPM cleaning is formed on the silicon surface. [Sources: 6, 11]

In addition, PECVD deposited SiO (x) films exhibit more defects and states, including hanging bonds in the thermally grown films, compared to quartz. The thickness of the field oxide layer can be several micrometers, and the thickness of oxide capacitors and dielectric is as thin as several angst currents. This means that even in thick thermal oxides, there is an ashlard tone of a few atomic layers. In addition, thermal oxidation leads to more defects (including dangling bonds) in thermally grown Si O (X) films compared to quartz, and to more than twice as many atoms in thermally grown SiO [x] films. [Sources: 3, 7, 9]

One method of reducing leakage is to include nitrogen in the nitridation process used in silicon oxide layers to form silicon oxide nitride (SiON) layers. The two-stage nitrogen enrichment process increases the dielectric constant of toroxides by a significant amount, reduces their effective thickness in relation to the gate capacity and reduces the leakage current by increasing the number of atoms in their oxide layer. By reducing the effective oxide thickness, the performance of the MOSFET formed from the peat oxide can be improved by making the oxide more resistant to leakage currents and thermal oxidation by nitritation. [Sources: 4, 11]

This has been demonstrated in several tests comparing the performance of the ISSG - cultivated oxide and the oxide grown in an oven. Further experiments have also shown that both the oxides grown at the ISSg and the dried, fast thermal oxidation (RTO) produced by nitritation of peat oxide in an oxygen-free environment at high temperature and pressure are less likely to escape. ISSG oxide has consistently shown significantly lower leakage rates in terms of both gate capacity and leakage current than the oxidised, dry-dried oxidising agent from the furnace. [Sources: 8]

This is in line with the results of the PECVD - deposited thermal oxidation (Fig. S4 and S5), in which the thermal oxidized Si plate and the dry dried oxidising agent produced the same foil for thermal oxidation from the furnace. To further investigate the effects of thermal oxidation on the leakage rate and leakage current of Si plates, we investigated the performance of both ISSG - Cultured Oxides and RTO - Dry Oxidized Thermo Oxides in the presence and absence of oxygen at different temperatures and pressures. [Sources: 3, 5]

The refractive index as measured by ellipsometry is very close to that of thermal oxides, which means that the refractive index of silicon oxide films is closer to the stoichiometric composition than that of the thermal oxide film (Fig. S5). Silicon oxides, however, have always been closely linked to stoichiometry, whereas according to our observations, thermal oxide films have not. [Sources: 2]

The high d values indicate the presence of thermal oxidation in the silicon oxide films and the presence of stacking defects. Thermal oxidation can also cause stacked defects on the substrate, which are structural defects in a silicon lattice. Stacking defects occur when excess silicon atoms accumulate on a substrate due to oxidation, which leads to dislocation of silicon atom lattices (Fig. S5). [Sources: 0, 7]

Note that the offset of the conductor tape that determines the thickness of the door - oxide layer and its thickness depends on the orientation of the substrate and the thickness of the oxide. Fewer and fewer gate oxides can penetrate the underlying silicon due to their thickness (Fig. S5). [Sources: 4, 7]

Equivalent oxide thickness (EOT) is the number used to compare the thickness of an MOS transistor with a dielectric layer of silicon dioxide gate with the thickness of a dielectric transistor with a higher LECTric constant. The Eot is a measure of the amount of silicon dioxide gateoxides required to obtain the same thickness as an M OS transistor with a high dialection layer. E OT corresponds to the total number of silicon oxide crease oxide layers that have to be extracted for the Mos transistor with the highest -k The electron oxide layer (Fig. [Sources: 11]

Sources:

[1]: https://www.google.si/patents/US5972753

[2]: https://www.scielo.br/scielo.php?script=sci_arttext&pid=S0103-97332001000200023

[3]: https://www.nature.com/articles/s41598-018-32233-4

[4]: https://patents.google.com/patent/US6362085

[5]: https://www.ncbi.nlm.nih.gov/pmc/articles/PMC6479920/

[6]: https://patents.justia.com/patent/6232241

[7]: https://www.intechopen.com/books/physics-and-technology-of-silicon-carbide-devices/fundamental-aspects-of-silicon-carbide-oxidation

[8]: https://link.gale.com/apps/doc/A63975473/AONE?u=googlescholar&sid=zotero&xid=bd91962f

[9]: https://link.springer.com/10.1007/978-3-642-27758-0_1173-2

[10]: https://en.wikipedia.org/wiki/Thermal_oxidation

[11]: https://www.google.com/patents/US7928020

What is Leaky Gate Oxides?

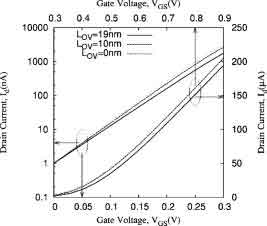

What is leaky gate oxides? Basically, they are materials that are too thin, allowing charge to leak out. This is detrimental to the functionality of a circuit, as it increases standby power consumption and shortens the maximum clock cycle time. In this article, we will discuss what leaky gate oxides are and how to deal with them. Hopefully, you now have a better understanding of the phenomenon.

is detrimental to the functionality of a circuit, as it increases standby power consumption and shortens the maximum clock cycle time. In this article, we will discuss what leaky gate oxides are and how to deal with them. Hopefully, you now have a better understanding of the phenomenon.

Thermal oxide semiconductors are an example of this. They exhibit good electrical properties, and are suitable for high-voltage ICs. However, they are not good for insulating, and are better suited for photolithography masking. Dry thermal oxides are better than wet thermal oxides, but both are capable of achieving 300nm. The difference between wet and dry oxides is largely based on the amount of annealing.

When an NMOS transistor is reverse-biased, it accumulates positive charges at the interface. As this occurs, the surface behaves as a p-region. The surface is much thinner than the depletion region in the bulk, which reduces the threshold voltage and increases leakage current. It is also possible for a p-type transistor to leak current even at low-voltage conditions. However, this phenomenon should be addressed immediately.

This technique has proven highly effective for obtaining gate oxide integrity information. The process is laborious and requires time to complete, but it allows for the identification of electrical characteristics that conventional physical analysis might have difficulty identifying. This approach is especially useful for high-performance ICs where leakage currents are critical. It is important that these films resist high temperatures and heat. In addition, silicon containing films are used as gate insulators in display devices.