Here we report an integrated lab-on-a-chip multilayer microfluidic platform to quantify the membranolytic efficacy of such antibiotics. The platform is a biomimetic

vesicle-based screening assay, which generates giant unilamellar vesicles (GUVs) in physiologically

relevant buffers on demand. Hundreds of these GUVs are individually immobilised downstream in physical

traps connected to separate perfusion inlets that facilitate controlled antibiotic delivery. Antibiotic efficacy

is expressed as a function of the time needed for an encapsulated dye to leak out of the GUVs as a result

of antibiotic treatment. This proof-of-principle study probes the dose response of an archetypal polypeptide

antibiotic cecropin B on GUVs mimicking bacterial membranes. The results of the study provide a

foundation for engineering quantitative, high-throughput microfluidics devices for screening antibiotics.

Double Side Polished (DSP) Silicon Wafers

We have a large selection of ultra-flat double side polished prime grade and test grade silicon wafers in all diameters, thickness, Ori and resistivities. We have Total Thickness Variations as tight as 1 micron TTV in stock.

In order to increase the flatness of a silicon wafer is to polish the back-side of the wafer. The double side polishiing helps reduce the roughness of the silicon wafer surfaces. This is a must when making MEMS devices where super flat and low roughness specs are required.

Get Your Quote FAST! Or, Buy Online and Start Researching Today!

Gettering and Double Side Polished Silicon Wafers

It is interesting to note that borosilicate (BSG) and phosphosilicate (PSG) glass when contacting heated silicon are very good at removing a silicon wafer's deep impurities.

Double Side Polishing a must fror ultra-thin-silicon wafers.

We can make single side polished silicon wafers to 50 micron with tight TTV, but thinner than this requires the more expensive back side polishing to keep the wafers from warping.

Use double side polished silicon wafers when you need tighter TTV, BOW and WARP tolerances.

Advantages of Double Side Polished Silicon Wafer Applications

Optical coherence tomography (OCT) is one of the most important tools used for manufacturing semiconductor components. Its accurate thickness measurements make it possible to manufacture high-quality Si wafers. The system is ideal for fabricating silicon devices such as high-frequency integrated circuits. It also helps improve the manufacturing process and is effective for a wide range of industrial applications

The most important characteristic of a double-sided polished silicon wafer is its improved performance. Its mirror finish eliminates microroughness and damage on the surface, which improves efficiency and reduces the risk of contamination. The process involves several steps that help ensure a high-quality and consistent finish. This article will outline the benefits of double-sided polishing and how it can benefit your business. It is a cost-effective option for semiconductors.

The primary advantage of double-side polished silicon wafers is their superior performance. Both sides of the wafer are polished to a mirror finish. As a result, the surface contamination is significantly reduced. This process is also effective at reducing the risk of particle trapping, which causes poor performance and inefficiencies. The polishing process also makes the silicon wafer thinner than a regular one, resulting in a single-ingot manufacturing method.

Double-sided polished silicon wafers are preferred over single-sided polished silicon. Their smooth, mirror-like surface provides the best surface quality for high-precision applications. Besides, these products are more expensive than double-sided polished silicon wafers, but they do not affect the quality of finished products. They are also available in smaller quantities than Double Side Polished Wafers. These double-sided silicon wafers are more durable and can be used in industrial-grade semiconductor manufacturing.

The double-side polished silicon wafer has a higher performance than regular silicon wafers. Its mirror finish reduces the amount of surface contamination, which is the primary cause of poor performance and inefficiency in semiconductor manufacturing. This product is more efficient and cost-effective than a regular silicon or a double-sided glass. Further, it is thinner than the regular silicon and can be produced in a single ingot.

A double-sided polished silicon wafer is the most widely used type of semiconductor. The process has several advantages. It is an effective way to reduce surface contamination and enhance throughput. Furthermore, it offers high levels of transparency. It also increases the surface's flatness. It is also a cost-effective method of processing semiconductors. It is highly customizable and flexible. The cost-effective way to create a custom-designed silicon wafer.

The benefits of double-sided polished silicon wafers are significant. The process improves the local flatness of the semiconductor. It also yields high yields. The resulting semiconductors have excellent flatness and a higher level of efficiency. These processes are costly, but they are very effective. For example, a single-sided polished silicon wafer is a good candidate for a multi-sided double-sided silicon wafer.

Double-sided polished silicon wafers are superior to unidirectional polishing. They have better surface contaminant resistance. A double-sided polished silicon wafer has a mirror-like finish. Its mirror-like finish is ideal for multiple applications. The process also reduces damages. In addition to improving the performance of semiconductors, the resulting double-sided polished silicon wafers are also less expensive.

In addition to these benefits, double-sided polished silicon wafers also provide improved electrical properties. The double-sided polishing process is highly advantageous for semiconductor applications, since it allows for a wide range of applications. Compared to single-sided polished silicon wafers, they are thinner and more flexible. In addition, their tighter TTV, BOW, and WARP tolerances are higher, enabling higher-quality semiconductors.

Double Side Polished Silicon Wafers for Lab-on-a-Chip Research

Research: A microfluidic platform for the characterisation of membrane active antimicrobials

UniversityWafer, Inc. Provided the following wafer spec:

100mm P/B (100) 1-10 ohm-cm DSP 500um Prime Grade

Below are just some of the double side polished wafers with the tightest TTV

The following are CZ Wafers unless otherwise noted. The wafers are SEMI prime with either a one or two flats or notch. The Total Thickness Variation is <1 μm, Bow <5μm, Warp, <10μm. All the wafers are Prime grade and are shipped in sealed hard plastic cassettes.

| Item | Type/Dop | Ori. | Dia(mm) | Thk(μm) | Polish | Res Ωcm |

|---|---|---|---|---|---|---|

| 6971 | n-type Si:P | [100-25° towards[110] ±1° | 6" | 675 | DSP | 1-100 |

| S5594 | P/B | [100] | 5" | 990 ±8 | DSP | 1-25 |

| D868 | P/B | [100] | 5" | 590 | DSP | 1-30 |

| F709 | n-type Si:P | [100] | 5" | 762 ±12 | DSP | 5-35 |

| S6284 | n-type Si:P | [100] ±1° | 4" | 200 ±10 | DSP | FZ >1,000 |

| G706 | Intrinsic Si:- | [100] | 4" | 500 | DSP | FZ >20,000 |

| 6356 | Intrinsic Si:- | [100] | 4" | 500 | DSP | FZ >20,000 |

| J302 | P/B | [100] | 4" | 600 | DSP | 1-50 |

| 7089 | P/B | [100] | 4" | 381 ±7 | DSP | 0.014-0.021 |

| F022 | P/B | [111] ±0.3° | 4" | 350 ±5 | DSP | <0.05 |

| 6570 | n-type Si:P | [100] | 4" | 400 | DSP | 1-10 |

| 4975 | n-type Si:Sb | [211] ±0.5° | 4" | 1,500 ±15 | DSP | 0.01-0.02 |

| S962 | Intrinsic Si:- | [100] | 4" | 525 | DSP | FZ >20,000 |

| D796 | P/B | [100] | 4" | 500 | DSP | 1-30 |

| L302 | P/B | [100] | 4" | 625 | DSP | 1-50 |

| Q787 | P/B | [111] ±0.5° | 4" | 350 | DSP | 0.001-0.005 |

| J066 | n-type Si:P | [100] | 4" | 500 | DSP | 1-100 |

| 4154 | P/B | [110] ±0.5° | 3" | 360 | DSP | 1-10 |

| 6826 | P/B | [100] | 3" | 475 | DSP | 1-50 |

| D750 | P/B | [100] | 3" | 420 | DSP | <1 |

| S5580 | n-type Si:P | [100] ±1° | 3" | 2,286 ±13 | DSP | 15-28 |

| S5824 | n-type Si:P | [100] ±1° | 3" | 300 ±10 | DSP | 5-15 |

| 6400 | n-type Si:P | [100] | 3" | 350 | DSP | 1-25 |

| 6818 | n-type Si:P | [100] | 3" | 381 | DSP | 1-30 |

| H988 | P/B | [100] | 3" | 580 | DSP | 1-100 |

Double Side Polished Silicon Wafer Research

![]() The double side polished silicon wafer process is an ideal solution for producing high-quality, high-contrast devices. The process can produce a large number of fine and very fine features. The process can be automated and requires only minimal human intervention. The DSP system can polish Si wafers up to 300mm in diameter. The system features an elaborate DSP system with thickness feedback control. The laser probe is placed on the upper plate and rotates at preset speeds, resulting in a planetary motion that polishes the Si wafer's surface.

The double side polished silicon wafer process is an ideal solution for producing high-quality, high-contrast devices. The process can produce a large number of fine and very fine features. The process can be automated and requires only minimal human intervention. The DSP system can polish Si wafers up to 300mm in diameter. The system features an elaborate DSP system with thickness feedback control. The laser probe is placed on the upper plate and rotates at preset speeds, resulting in a planetary motion that polishes the Si wafer's surface.

Double side polished silicon wafer research involves fabricating a wafer from two opposite sides. The technique involves forming and estimating the thickness of the Si wafer by using optical coherence tomography. The method used in this paper involves placing a laser probe on a silicon wafer surface. The researchers then used an updated B-spline model based on measurement points. The model predicts the thickness of the polishing layer on the other side of the wafer. As a result, residual errors are treated as random errors, reducing the chances of erroneous measurements.

The precise location of the laser probe on the silicon wafer surface is crucial to the measurement of the double side polished silicon wafer. In addition, the system must maintain the extrinsic gettering capabilities of the silicon. This makes it a highly efficient tool in semiconductor manufacturing. So, the double side polished silicon technology is here to stay. This new process will make it easier for semiconductor producers to produce high-quality semiconductors.

As a result, the double side polished silicon wafer research will help manufacturers create high-quality, low-cost silicon wafers. In addition to making electronic products cheaper and better, this technology will help protect the environment. The production of high-quality wafers will not only improve performance but also make electronics safer and more environmentally friendly. It will be a great investment for everyone involved. With the advancement in this field, we will be able to make a better quality semiconductor.

The double side polished silicon wafer is one of the most important types of semiconductors. The double-side polishing process requires both extrinsic and intrinsic gettering capabilities. Hence, it is important to maintain these properties in order to maximize the performance of a device. It is also necessary to improve the efficiency of the double-sided polishing process by improving the cost of manufacturing. A higher cost-effectiveness can be realized by the development of a device if it uses the correct techniques.

In the double side polished silicon wafer process, the dual surface polishing method is necessary for a semiconductor to retain its extrinsic gettering capabilities. In addition to these features, it is also important to optimize the self-rotating grinding process to increase the yield and minimize the machining time of the double side polished silicon wafer. The process of the double-side polished silicon wafer has been known for decades.

The invention of the double-side polished silicon wafer process was first described in the literature by Schwandner et al. In addition to their presentation of the construction of the double-sided polished silicon wafer, they also presented a mathematical model of the effects of different pre-polishing processes on the thickness of the silicon wafer. Furthermore, by analyzing the thickness of a double-sided polished silicon sphere, the researchers were able to determine the thickness of the evaporating SiO2 layer.

The double-side polished silicon wafer research results show that it is possible to manufacture a silicon wafer with high-quality and low-cost. The process will help manufacturers produce more affordable, high-quality electronic products. The ICMI research will also be beneficial to the environment because it will reduce the use of chemicals. This will save the environment and help consumers and businesses alike. If the double-sided polished silicon is developed, it will be more likely to be environmentally friendly.

The size of single side polished silicon wafers has become increasingly important. They are typically around 50 microns thick. Because they are thinner, the backside polishing is necessary to prevent warping. The double-sided polished silicon is more expensive and requires more labor, but the cost is much lower than single-sided polished silicon. The research involves the use of a unique process called lapping. There are several advantages to both processes.

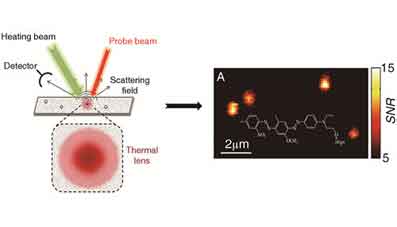

What Silicon Wafer Spec is Used for Background Noise Suppressed High-Throughput Mid-Infrared Photothermal Microscopy via Pupil Engineering

Photothermal Microscopy is a technique that allows the detection of nanometer-sized objects solely  based on their absorption. This technique is particularly useful for observing gold nanoparticles within cells. This method has numerous applications in analytical chemistry, bioimaging, and spectroscopy. Read on for a closer look at this process. Its advantages include high sensitivity and low cost. Here are some of the most popular applications.

based on their absorption. This technique is particularly useful for observing gold nanoparticles within cells. This method has numerous applications in analytical chemistry, bioimaging, and spectroscopy. Read on for a closer look at this process. Its advantages include high sensitivity and low cost. Here are some of the most popular applications.

Scientists used the following DSP Silicon Wafers from UniversityWafer, Inc. for their research.

Si Item #1115

100mm P/B (100) 10-20 ohm-cm 500um DSP Prime

"A 4" double-side polished silicon wafer with 500 µm thickness (University Wafer) is diced to 10 mm × 20 mm pieces."

Wafers used in Non-biofouling materials prepared by atom transfer radical polymerization grafting of 2-methacryloloxyethyl phosphorylcholine: Separate effects of graft density and chain length on protein repulsion Research

Double-side polished silicon wafers (P-doped, (100)-oriented, 10–20 ohm-cm resistivity, 0.56mm thickness) werepurchased from University Wafer, Inc.

What is Graft Polymerization?

Basically, graft polymerization is a method of converting macromolecules into polymers by combining monomers into a chain. The grafted copolymer is composed of chains of different molecular weights, with the distribution of grafts affecting its physical properties. The polymer is derived from acrylate functionalized monomers or free radicals. The amount of chains grafted depends on the ratio of molar concentration of the monomer and macromonomer.

In the "grafting through" process, a low-molecular-weight monomer is radically copolymerized with a macromonomer prepared by another controlled polymerization process. This technique allows the incorporation of a variety of monomers into polymers, including polyethylene into a polystyrene backbone, and poly(ethylene oxide) into a styrene-based material.

Often, grafting aims to improve other properties of conducting polymers beyond charge transport. The grafted polymer can have improved solubility, nano-dimensional morphology, and biocompatibility. Grafted polymers are also more biocompatible and capable of achieving communication with cells. These are all advantages that are not possible with conventional polymers, which are often visible in biomedical and industrial sectors.

A film-based electrolyte membrane is prepared by three steps: crosslinking, grafting by Preirradiation, and sulfonation. In a schematic view, graft polymerization has a crystalline domain where the long-living radical accumulates. The amorphous domain has monomers accessible to the long-lived radical. All three of these steps occur at the interface of the two films.

Related Silicon Wafer Finish and Specification Resources

DSP Silicon Wafers: When to Use Double-Side Polishing for Tighter TTV, Bow, and Warp

Polished Silicon Wafers: Single-Side Polished vs. Double-Side Polished

High-Quality Silicon Wafers: Key Specs Explained (TTV, Flatness, CZ/FZ, and More)

Undoped Silicon Wafers: SSP and DSP Options for Research

(100) Orientation Silicon Wafers: Selection and Common Use Cases