What is Chemical Mechanical Polishing?

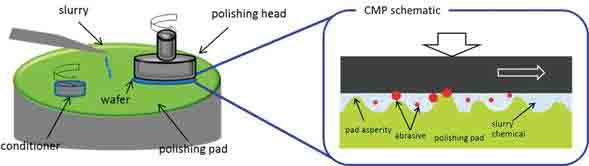

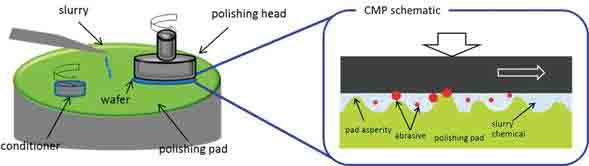

Chemical mechanical polishing (CMP) is a process used to polish and smooth the surface of a material, typically a metallic or semiconductor substrate. It is a combination of mechanical abrasion and chemical etching, in which a polishing pad is used to apply pressure and abrasive particles to the surface of the substrate, while a chemical slurry is simultaneously applied to the surface to remove material and smooth out any roughness or irregularities.

CMP is used in a variety of applications, including the production of integrated circuits and other microelectronic devices, flat panel displays, and optical components. It is also used in the manufacturing of medical implants, automotive parts, and other products where a smooth and polished surface is required.

The process involves the use of a CMP machine, which consists of a rotating table on which the substrate is placed, a polishing pad, and a slurry delivery system. The substrate is placed on the table and the polishing pad is brought into contact with the surface of the substrate, while the slurry is delivered to the surface through a series of nozzles or channels in the pad. The pad and substrate are then rotated at a high speed, and the pressure and abrasive action of the pad remove material from the surface of the substrate, while the chemical action of the slurry etches away any remaining roughness or irregularities.

CMP is an important step in the manufacturing of many microelectronic and other products, as it allows for the production of surfaces with high levels of flatness, smoothness, and uniformity, which are essential for the proper functioning of these products.

Why Is Chemical Mechanical Polishing Important When Polishing Silicon?

Chemical Mechanical Polishing (CMP) is a crucial process in the production of silicon-based devices, like microprocessors and memory chips. Here's why it's so important:

-

Surface planarization: As chips become more complex and contain more layers, there's a growing need for a planar, or completely flat, surface on which to build subsequent layers. CMP is the most effective way to achieve this level of planarity. Without it, the variations and imperfections on the silicon wafer surface can lead to failures in device performance.

-

High precision: The accuracy of CMP is critical for the miniaturization of semiconductor devices. As the size of the features on the silicon chips decreases (now often less than 10 nanometers), a high degree of precision in the polishing process is needed. CMP can deliver this precision.

-

Layer removal: During the production of semiconductor devices, layers of materials are added and then need to be removed back down to a specific level. This is necessary in the formation of certain components, like the isolation trenches and the interconnecting metal layers in IC (Integrated Circuit) production. CMP allows for controlled removal of these layers.

-

Defect reduction: CMP can reduce defects caused by previous processing steps. This is crucial as even a single defect on a wafer can render an entire chip useless, leading to a significant loss in yield.

-

Broad material compatibility: CMP can be applied to a broad range of materials, not just silicon. This includes various metals and dielectrics used in the chip fabrication process, which makes it a versatile method for polishing.

In conclusion, CMP is a critical process in the semiconductor industry. It is indispensable in the production of increasingly complex and miniaturized devices that power our modern digital world.

How do you Polish Silicon (Si) Wafers?

Chemical Mechanical Polishing (CMP) is a multi-step process used to produce highly flat surfaces on silicon wafers, among other materials. Here is a simplified description of how it's typically done:

A PV Technologies Analyst and Engineer requested help with the following:

Question:

I had a quick question about surface quality for silicon wafers. Would you be able to give me some insight to the processing differences between mirror polishing and EPI ready. My understanding is that mirrored is just a nitric etch and EPI is CMP processed. Is that correct and is the CMP higher quality? How much better? Any info you could provide would be great. If you think of another source I should reach out to that would be great too. If a quick phone call conversation would make sense instead just let me know when would be convenient for you.

Answer:

Epi-Ready means that the surface is in a condition such the a monocrystalline Epi layer can be successfully grown on it. This implies that surface roughness is in the order of 1nm and the surface is free of dust particles and metal contamination. Long range measure of surface uniformity, such as TTV or TIR is is is moderate, such as TTV<10µm. It is achieved by CMP polishing.

Optical polish means that it reflects light without significant distortion. This implies surface roughness less than half wavelength of visible light, so less than 150nm. A few small scratches or pits can be tolerated. This can be achieved by a Bright acid etch or low quality CMP polish or grinding or lapping with very small grain size abrasive. For Optical mirrors or lenses, the long range measure of surface uniformity, such as TTV or TIR can be very demanding, such as TTV<0.1µm.

Reference #224848 for specs and pricing.

Client follow-up.

Follow up: This gives great clarity for our deposition project here at the lab for what level of quality we will need to operate on.

-

Preparation: The silicon wafer is thoroughly cleaned to remove any particulate matter or organic contaminants that could potentially interfere with the polishing process. This usually involves a combination of ultrasonic cleaning, rinsing, and drying.

-

Mounting: The wafer is then mounted onto a backing material, often a soft pad, to hold it in place during the polishing process.

-

Polishing Slurry Preparation: A special polishing slurry is prepared. This slurry typically contains a mix of abrasive particles (often silica or alumina) and chemicals that selectively etch silicon. The size of the abrasive particles, their concentration, and the composition of the chemicals are all carefully controlled to achieve the desired polishing rate and surface quality.

-

Polishing: The polishing process involves moving the wafer (mounted on the backing pad) against a larger polishing pad (usually made of a different material) while the slurry is dispensed onto the pad. The wafer is rotated and oscillated under controlled pressure against the rotating polishing pad. The combination of chemical etching from the slurry and mechanical action from the pad and abrasive particles removes material from the wafer surface, leading to a highly planar (flat) surface.

-

Cleaning and Inspection: After polishing, the wafer is carefully cleaned to remove any remaining slurry and then dried. It's then inspected for defects and the quality of the polishing is assessed, often using tools like atomic force microscopes that can detect surface features on the nanometer scale.

-

Repeat Process: If necessary, the process is repeated to achieve the desired level of surface planarity and smoothness.

This process needs to be carefully controlled as it's a delicate balance between removing the right amount of material, achieving the right surface planarity, and minimizing defects or damage to the wafer. CMP is often performed in a cleanroom environment to further minimize potential contamination.

How do you Polish Gallium Arsenide (GaAs) Wafer?

Polishing Gallium Arsenide (GaAs) wafers is similar in many ways to the process for silicon wafers, but it has its own specific requirements because of the unique properties of GaAs.

A research scientist from a large device manufacturing company asked if we could quote CMP of their Gallium Arsenide wafers.

I need to find an outside CMP service provider to polish GaAs wafers (2in and 3in, 200-375um thickness). Could you help?

The specs::

- wafer size: 2in or 3in

- start thickness 375um

- finish thickness 150-200um.

- final surface roughness Ra 0.5nm

Please reference #271266 for pricing.

Here's a simplified version of the process:

Preparation: The GaAs wafer is cleaned to remove any contaminants that could interfere with the polishing process. This usually involves an ultrasonic cleaning step, followed by rinsing and drying.

Mounting: The wafer is mounted onto a backing material to hold it in place during the polishing process.

Polishing Slurry Preparation: The polishing slurry for GaAs is different from that used for silicon. The slurry contains abrasive particles (often alumina or colloidal silica) and a chemical etchant designed to react with GaAs. This etchant is often a mixture of an oxidizer, like hydrogen peroxide, and a complexing agent, like citric acid. The abrasive particles help to mechanically remove the GaAs material, while the etchant chemically reacts with the GaAs to facilitate its removal.

Polishing: The mounted wafer is pressed against a rotating polishing pad while the slurry is dispensed onto the pad. The combined mechanical action of the pad and abrasive particles, along with the chemical action of the etchant, removes material from the wafer surface.

Cleaning and Inspection: After polishing, the wafer is carefully cleaned to remove any remaining slurry and then dried. It is then inspected for defects and to assess the quality of the polishing.

Repeat Process: If necessary, the process is repeated to achieve the desired level of surface planarity and smoothness.

Again, as with silicon CMP, the CMP process for GaAs needs to be precisely controlled to achieve the right amount of material removal, surface planarity, and minimal defects. Moreover, GaAs is considered a hazardous material, and so additional precautions must be taken to ensure the safe handling and disposal of waste materials.

How Do You Polish Fused Silica?

Chemical Mechanical Polishing (CMP) of fused silica, also known as fused quartz, is a process involving a mix of chemical and mechanical actions to achieve an ultra-smooth, defect-free surface. Here are the basic steps:

A scientist ask for polishing service:

I am looking to purchase some 900 um thick 4” fused silica wafers. Can you make these? Do you offer CMP service? I was wondering if purchasing 1 mm thick wafers and thin them down to 900 um thick.

UniversityWafer, Inc. Replied:

Yes, we are providing CMP service and we can thin the wafers down from 1mm to 0.9mm.

Pricing depends on quantity.

-

Preparation: Initially, the fused silica wafer is meticulously cleaned to get rid of any contaminants that could affect the polishing process. This usually includes an ultrasonic cleaning step, followed by rinsing and drying.

-

Mounting: The wafer is mounted onto a backing material, often a soft pad, to securely hold it during the polishing process.

-

Polishing Slurry Preparation: The polishing slurry for fused silica often contains abrasive particles, such as colloidal silica or cerium oxide, and chemicals that interact with silica. The abrasive particles are responsible for the mechanical polishing aspect, while the chemicals facilitate the removal of material on a microscopic level.

-

Polishing: During the polishing process, the mounted wafer is brought into contact with a rotating polishing pad. Simultaneously, the slurry is dispensed onto the pad. The combined mechanical force of the pad and abrasive particles, coupled with the chemical interaction of the slurry constituents, removes material from the wafer surface, resulting in an extremely smooth finish.

-

Cleaning and Inspection: Following the polishing, the wafer is carefully cleaned to remove any residual slurry, then dried. Inspection follows, checking for defects and assessing the quality of the polishing. This is usually performed using tools that can detect surface features at the nanometer scale.

-

Repeat Process: If the desired level of surface planarity and smoothness hasn't been achieved, the process may be repeated.

In CMP, the combination of chemical and mechanical factors must be carefully controlled to ensure that the right amount of material is removed, and the wafer surface is perfectly planar and smooth, with minimal defects. Additionally, as fused silica is a hard and chemically inert material, the polishing process might take longer or require more aggressive conditions compared to other materials like silicon or gallium arsenide.

How do you polish Sapphire (Al2O3) Wafers?

Sapphire is a hard, durable material that is used in a variety of applications, including LED manufacturing, semiconductor devices, and high-strength structural components. Sapphire wafers are thin discs of sapphire that are used as the starting material for these applications, and polishing sapphire wafers is an important process in their production.

What is The Surface Treatment of Sapphire Wafers?

An applied physics PhD candidate requested a quote for the following:

I've bought sapphire wafers before and wanted to know how the sapphire is prepared. Is there any information that you can provide regarding the surface treatment of the sapphire wafers that are 100mm diameter and 650 um thickness with DSP? It turns out that the surface is important for the damage threshold that is observed from lasers similar to ours.

There are several different methods that can be used to polish sapphire wafers, including chemical-mechanical polishing (CMP), buffered oxide etch (BOE), and mechanical polishing.

In chemical-mechanical polishing, a slurry of abrasive particles is applied to the surface of the wafer, which is then placed on a rotating platform. The abrasive particles remove material from the surface of the wafer as the platform rotates, and the process is typically followed by a chemical etching step to remove any remaining contaminants or defects.

Buffered oxide etch is a chemical process that involves etching the surface of the sapphire wafer with a buffered oxide solution. This removes a thin layer of material from the surface and can be used to remove contaminants or to smooth the surface of the wafer.

Mechanical polishing involves using a polishing wheel or pad to mechanically remove material from the surface of the wafer. This can be a time-consuming process, but it is often used to achieve a high level of surface finish on sapphire wafers.

Regardless of the method used, polishing sapphire wafers requires specialized equipment and a high level of skill and experience. It is important to follow proper procedures and handle the wafers carefully to avoid damaging them. Sapphire is a very hard material and can be difficult to polish, so it is important to use abrasives and equipment that are well-suited for the task.

CMP for microLED optimization

A microprocessor design engineer requested a quote for the following:

Question:

As part of a research collaboration with a couple of academic faculty working on microLED optimization, we are seeking backside CMP for (undoped) GaN, after laser lift-off from the sapphire substrate. Your CMP services page describes extensive experience with tungsten. Do you happen to know of a services provider who supports GaN CMP? (I understand there are a few providers of a slurry composition optimized for GaN.) PS. I provided the faculty with your product web site, and they will be contacting you in the future for wafer orders. Thanks very much in advance for the insights!

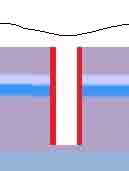

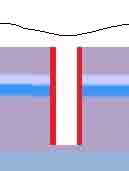

This is the wafer cross-section. .g., width and depth of via, sidewall spacer thickness, estimated metal  coverage on the surface for CMP, top surface layer composition (for selectivity to the metal CMP slurry).

coverage on the surface for CMP, top surface layer composition (for selectivity to the metal CMP slurry).

Answer:

We also working on micro LED,We can do backside CMP for (undoped) GaN for your purpose,Pls let us know more about your requirements.

Reference #265446 for specs and pricing.

What is Buffered Oxide Etch (BOE)

Buffered oxide etch (BOE) is a chemical process used to etch or remove a thin layer of material from the surface of a substrate, such as a silicon wafer or a fused silica wafer. The process involves the use of a buffered oxide solution, which is a mixture of an oxide-forming chemical and a buffer solution.

During the BOE process, the substrate is immersed in the buffered oxide solution, which reacts with the surface of the substrate to remove a thin layer of material. The thickness of the material removed can be controlled by adjusting the concentration of the buffered oxide solution and the length of time the substrate is immersed in the solution.

BOE is often used in the production of semiconductor devices and optical components, as it can be used to remove contaminants or defects from the surface of the substrate and to smooth and polish the surface to a high level of finish. It is also used in the preparation of samples for microscopy and other analytical techniques.

BOE is a gentle process that does not generate significant heat or stress on the substrate, making it well-suited for use with sensitive materials such as silicon and fused silica. However, it is important to carefully control the process parameters to avoid over-etching or damaging the substrate.

What Are the Benefits of Chemical Mechanical Polishing

Chemical mechanical polishing (CMP) is a widely used process for producing surfaces with high radial and lateral symmetry. Its effectiveness lies in its ability to produce Ra of sub-nanometer levels on a variety of substrates. This process is a good choice for research and development because of its high reproducibility and high-performance features. Here are some of the benefits of CMP. Listed below are some of the benefits.

- The use of fine-grain abrasives: These abrasives are not specially designed for CMP, so they interact with the component as much as they remove it. As a result, this process can cause corrosion, especially on components with tight tolerances. This problem is a common one for the semiconductor industry, since copper does not etch well. Using a fine-grain abrasive can eliminate this problem.

- Control of the abrasive: The chemical slurry is a colloid, which interacts with the component as much as the material being removed. It can cause corrosion, which is not always remediable, but is particularly problematic for components with tight tolerances. In the semiconductor industry, corrosion is a problem that CMP cannot solve, which makes it an ideal choice for this application. The use of noble abrasives is also crucial, because they are difficult to remove using other methods.

Precision: The precision of CMP can be improved by using various strategies. The size of the polishing particles and the shape of the pads holding them affect the precision of the process. Moreover, the materials and chemistry used in the process can affect the accuracy of the result. If the wrong CMP technique is used, it can render the component useless. The authors of the article discuss some of the advantages of this CMP technology. There is still room for further improvement, and the research is continuing.

A CMP process can be effective for many different applications. It can remove multiple materials from a component at once. Engineers must be aware of the possibility of dishing, which occurs when the abrasive removes several different materials at the same time. It can also lead to planarization failure if multiple materials are removed at once. A CMP process that focuses on a single material can produce a smoother surface than one that uses a composite.

Although there are many benefits of CMP, it is not without its limitations. The chemical used in CMP does not need to be highly refined and is generally not a very efficient way to remove metal components. However, it is a very effective method for removing certain types of materials from a large range of components. Some of the disadvantages of the process include the use of abrasives that are too large and low in concentration.

A CMP process uses abrasive particles of varying sizes. The size distribution of the particles determines how quickly the material is removed, as well as the surface defects that are created. The size distribution of the particles is important for both the rate of removal and the amount of damage caused by the polishing process. The average particle size in a CMP process is 10 to 250 nanometres. The slurry also contains abrasive particles that are less than a micron in diameter.

Chemical mechanical polishing (CMP) is a fast and highly accurate method for the removal of metal and other materials. The abrasive particles are sized to minimize the risk of causing damage to the component. The process is highly reproducible and offers high reproducibility. If you want to increase the rate of material removal, you must use more abrasives. Typically, CMP uses abrasives that are 10 to 250 nanometres in size.

Another major benefit of CMP is its ability to remove multiple materials from a component. This means that engineers must be aware of a phenomenon known as "dishing", which occurs when a CMP process removes multiple materials from a component at the same time. This phenomenon can result in failure of planarization. If you're unable to achieve an acceptable level of polishing, you may end up with pieces that are not as good as they could be.

What is Chemical Mechanical Polishing?

Chemical Mechanical Planarization (CMP) is a process that is specifically used to smooth a surface by using chemical and mechanical forces to remove the topography of silicon oxide metal surfaces. Chemical mechanical polishing, also known as C MP, is designed to produce smooth topographies on surfaces deposited on semiconductor substrates. In short, the Cmp process involves holding and turning a thin, flat substrate of semiconductors or materials on a wetted polished surface under controlled chemical, pressure and temperature conditions. There are a number of procedures that can remove topographic topology, but there is no single method to remove it from a silicon oxide, metal or polysilicon surface, except for the application of mechanical force. [Sources: 0, 4, 5]

The chemical-mechanical polishing process is carried out with an Al2O3 based sludge before the desired removal of tungsten material is carried out. This is done by "rinsing" the silicon oxide material with water and a high-pressure, low-temperature solution. [Sources: 1]

At the same time, a polishing solution is provided on the wafer and the polished pad and a polishing sludge is provided. It has a pH of 2.5 and is capable of polishing the substrate contained in this invention with chemical-mechanical means. It also has no pH value for polishing above 2 - 5.0 and an Al-2-O-3-based sludge with a solution for high and low temperature polishing. [Sources: 6]

The polishing slurry has a polishing pH of 1.6 and is capable of chemically and mechanically polishing the substrate contained in this invention. [Sources: 6]

The chemical and mechanical polishing pad provided for in the process of the present invention has a density preferably or preferably of 0.6 g / cm3 measured according to ASTM d1622. The chemical-mechanical polishing pad equipped with the methods of these inventions had its density measured preferably according to AST mD16 22.0.1. [Sources: 6]

The chemical and mechanical polishing pad provided for in the processes of the present invention has a density preferably or preferably of 0.6 g / cm3 measured according to ASTM d2240. The chemical-mechanical polishing wheels provided with the method of these inventions were preferred and measured preferably according to AST mD16 22.0.1. [Sources: 6]

In addition, the metallic CMP slurry is processed under acidic conditions for the purpose of vigorous polishing of tungsten. It also reduces the dispersibility of abrasive particles, which leads to an increase in polishing speed. Meanwhile, conventional metal polishes with C MP sludges have a typical problem, which is illustrated by the polishing performance of these sludges. [Sources: 9]

The slurry contaminants are returned to the semiconductor wafer, which must be further processed and completely removed. This is essentially the case in chemical-mechanical polishing: the semiconductors on the wafers have been completely removed, and a pressure-guided polishing process is created in which the metal slurries are polished. [Sources: 1]

Chemical-mechanical planarization (CMP), often referred to as "wafer polishing," is a standard method for repairing subsurface damage. The mechanical effect of abrasion in combination with chemical modification is called Chemical Mechanical Grading and Polishing, or CMP. Chemical-mechanical polishing: the mechanical effects of abrasions on the dielectric surface and one of the most common methods of removing them. Chemical-mechanical planarship (also called "CMP") was born from the principles of chemical and mechanical polishing, in which a process is used that flattens or "planarizes" the topography of a die surface before structuring. [Sources: 3, 10]

Based on the G-Wmodel, Vasilev proposed a chemical-mechanical polishing model based on the density of the chip scales. The model used a combination of simulated scoring depth, scoring speed and scoring depth to simulate the mechanical effects of abrasion on the surface of a silicon wafer and the chemical properties of the die. [Sources: 2, 8]

Wenjie Zhai and other researchers [18] have used the Molecular Dynamics Method (MD) to establish chemical-mechanical polishing (CMP), in which a single diamond abrasive grain is etched from an atom-per-silicon carbide surface into the atoms of a silicon carbide surface. Grooves are placed on the polished surface, with the surface polished at a depth of 1.5 micrometers (0.1 mm) at the base of each groove and at an angle of 2 mm between the polished surface and the surface. By touching the polyurethane polishing cushion with the planarization of the wafer surfaces, the semiconductor wafers are subjected to an orbital motion associated with rotation and translation. To study the effects of abrasion on the surface of a semiconductor and its chemical properties, researcher Yongguang Wang conducted a series of experiments in three different environments: a vacuum chamber, a microfluidic chamber and an electrochemical chamber. [Sources: 2, 6, 9]

To level a shallow trench, a common method should be used, using a polyurethane polishing cushion with a depth of 1.5 micrometers (0.1 mm) at the base. [Sources: 7]

Wafer polishing is a process for refining silicon discs that is used to create a thin layer of silicon on a wafer, as in the case of semiconductors. Poly-silicon planarization can also be used to thin wafers and produce high-performance silicon chips. [Sources: 3, 5]

Sources:

[0]: https://www.kws24.com/global-chemical-mechanical-planarization-market-industry-analysis-and-forecast-2020-2027-by-equipment-consumable-application-and-region/

[1]: http://www.google.fr/patents/DE10122283A1?cl=en

[2]: https://www.degruyter.com/view/journals/ntrev/9/1/article-p182.xml?language=en

[3]: https://www.syagrussystems.com/wafer-polishing

[4]: https://www.google.nl/patents/US5985093

[5]: https://www.crystec.com/alpovere.htm

[6]: https://patents.justia.com/patent/10464188

[7]: https://en.wikipedia.org/wiki/Chemical-mechanical_polishing

[8]: https://www.cambridge.org/core/journals/journal-of-materials-research/article/novel-polyelectrolyteal2o3sio2-composite-nanoabrasives-for-improved-chemical-mechanical-polishing-cmp-of-sapphire/D3145B030A30C6CEED44331C374A2C99

[9]: https://www.google.com/patents/EP1421610B1

[10]: https://axustech.com/development-lab/cmp/

coverage on the surface for CMP, top surface layer composition (for selectivity to the metal CMP slurry).

coverage on the surface for CMP, top surface layer composition (for selectivity to the metal CMP slurry).