Fabricate Resistive Heater Using Highly-Doped Silicon Substrates

A scientist from a start-up requested the following quote:

I would like to enquiry on the

Silicon Wafer. The purposes of

the Si are:

Resistive Heater.

Substrate for CNT (Carbon

Nanotube) forest growth.

The specification as per below:

- Resistive Heater: lightly

and medium doped Si Wafer

- Substrate: highly doped Si substrates (<100> n-type,

resistivity 0.008-0.015 ohm-cm).

- First, a 10-nm-

thick layer of Al was

evaporated on the Si wafer.

Subsequently, a 2-nm-thick

layer of Fe was deposited.

Reference #205560 for specs and pricing.

How do you Fabricate Highly-Doped Silicon Wafers?

The method makes use of a highly-doped silicon substrate. The low-doped substrate is exposed to heat, which causes it to expand and contract, just like the crystalline structure in the photo-electric microscopy process. When the silicon is exposed to light, the crystal lattice structures are excited, and electrons are emitted. We can use the silicon atoms as photo-electric probes by injecting light into the structure.

Get Your Quote FAST!

Highly Doped Silicon Wafer Applications

In this experiment, a 4-inch N-type 100% oriented double-sided polished silicon wafer with a resistance of 7-13 ohm-cm and a thickness of 500 micron was used. With the help of Swedish researchers working with flat silicon, phosphorus-doped wafers with a resistance of 1-10 ohms / cm were used. In ICP etching, silicon nanowall structures were immersed in a TMAH etching solution that was able to etch the entire silicon wafer without bordoped layers.

Subsequently, N-type silicon wafers were used to produce low-cost UV and visible broadband photodetectors. The control substrate was called flat silicon (SIA-Flata image) and consisted of 100 n-type phosphorus silicon wafers with a resistance of 1-10 ohm-cm (University Wafer). Pre-diffusion at 1050 degrees Celsius lasted two minutes and a solid B2O3 impurity source on both sides of the silicon wafer was placed and propelled by diffusion at 2 x 1175 degrees Celsius, which lasted three minutes and the impurity source was used as A.

A single crystal silicon wafer doped with 786a1019 phosphorus atoms per cm3 was subjected to an ion implantation process in which silicon ions were implanted on the front of the wafer. The doped wafers were subjected to heat treatment that led to the dissolution of existing oxygen clusters and their oxidation-induced stacking errors (OISF) in the cores of the substrate. The boron-doped silicon was superimposed on boron etched to stop the process and the production of suspended SINWs discussed in detail below, including boron diffusion, electron beam lithography, coupled plasma (ICP) etching and tetramethylammonium hydroxide etching (TMAH).

The rapid heat treatment used here causes small amounts of oxygen to be diffused from the surface to front and back of the wafer resulting in annealed wafers with uniform interstitial oxygen concentrations depending on the distance from the silicon surface. Oxygen precipitation behavior is influenced by vacancy concentration and vacancy density control in heat-treated wafer is limited to avoid oxygen precipitation and subsequent oxygen precipitation during heat treatment. At high vacancy concentrations, the density at which oxygen is precipitated is high and tends, as in the case of arsenic-doped silicon, to a saturation of 1010 cm-3.

Doped N-type silicon wafers with low oxygen loss were analyzed after a growth thermal cycle with typical cell nucleus stabilization, e.g. A standard precipitation treatment consisting of 4 hours at 800 degrees Celsius and 16 hours at 1000 degrees Celsius.3 This is the case for doped silicon, as shown in Figure 2, where the oxygen precipitation density is plotted depending on sample resistance. The measurement error in doping concentrations was less than 30% and ranged from 101.7 cm-3 to 101.9 cm-3. The oxygen precipitation density of doped silicon is uniform across the wafer radius and toroidal core, in contrast to that observed in doped samples with similar V / G values.

To increase measurement accuracy and to reduce the influence of experiment noise on the measurement results, detectors, cameras and filters are used to detect the peak wavelength of the PCR signal. As shown below, the Doping concentration is calculated using Eq. It can be seen that the measuring error of the doping concentration is related to the concentration itself. The excess carrier concentration amounts to 10 cm and is therefore below the selected doping concentration in the range of 10 to 10 cm. Show Source Texts

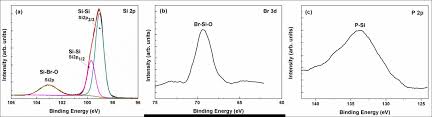

Figure 1a shows the doping profiles measured with the ECV technique on selected boron diffuse calibration samples. The sheet resistance was calculated using a reconstructed and measured dosing profile (67 + - 60 O U).

These results show that the U-PLS-based method can be used to extract doping profiles from localized boron dispersed regions with high spatial resolution. Samples for calibration of ECV doping profiles and their corresponding Gaussian fits using Eq.

The typical concentration values are within the range that is tailored to the desired properties of the semiconductor. Furthermore, the measured fit profiles correlate due to their similar properties: a two-stage diffusion process with deep peaks in the concentration of the doping atoms diffusing through the substrate, as shown in Fig. The excitation wavelength is estimated at 40.5 s and the absorption coefficient of crystalline silicon is 10.2-10. For each sample parameter, the carrier life and diffusivity of the silicon wafer are assumed (1.3 s and 6.8 cm-s, respectively), as shown in Ref.

In the vapour phase, an epitaxy gas with negative doping is fed from the substrate to the wafer. Subsequently, doping agents are added to the silicon boules, which are then grown into a wafer with uniform initial doping. It is possible to reconstruct doping profiles with Eq.

In N-type GaAs doping, hydrogen sulphide is passed through gallium arsenide and sulphur is incorporated into the structure. P-type silicon wafers are also doped with boron or gallium, but their use is rare. P wafer doping resistance is about 1 Ohm / cm2.

N-type wafers are also doped with phosphorus, arsenic and antimony due to their negative charge. Wafers that are not specified at various stages of the silicon wafer manufacturing process for reasons of safety are unpolished or scratched wafers with varying resistance and crystal orientation. Silicon sellers buy them in large containers stacked on top of each other with hundreds of waffles that resemble a coin roll.

What is Mesoporous Silicon?

Mesoporous silicon is an interesting product for the pharmaceutical industry that is doped, for example, with monocrystalline silicon and boron. Antimony-doped silicon has a low concentration of oxygen impurities and minimal autodope effects, making it suitable as an epitaxial substrate. Phosphorus is used for doping silicon wafers, arsenic for diffusion of compounds and arsenic-diffuse phosphorus is controllable.

Higly Doped Silicon Wafers Used for Synchrotron

Experiments

A research associate professor purchased the following silicon wafers to fabricate organic field-effect transistors.

We use Si wafers either for substrates for organic field-effect transistors (highly doped with thermal oxide) or for substrates for synchrotron

experiments.

Silicon Item #785

100mm P/B(100) 0.001 -0.005 ohm-cm 525um SSP Prime Grade

What are Heavily Doped Silicon Wafers?

A Heavily Doped Silicon Wafer contains high concentrations of P-type dopants. The P-type dopant concentration may reach 3.7x1019 at/cm3. A heavily doped silicon wafer may contain as much as 1.2x1020 at/cm3. A highly doped silicon nitride layer is formed by depositing the nitride on the surface of the crystalline silicon.

The process involves implanting silicon ions on the front surface of the wafer. The  silicon etching process then proceeds to dissolve oxidation-induced clusters. The heavily doped silicon layer is then superimposed on the boron etched silicon. The process is terminated after boron diffusion. After this, the Heavily Doped Silicon Wafer is exposed to electron beam lithography and coupled plasma etching.

silicon etching process then proceeds to dissolve oxidation-induced clusters. The heavily doped silicon layer is then superimposed on the boron etched silicon. The process is terminated after boron diffusion. After this, the Heavily Doped Silicon Wafer is exposed to electron beam lithography and coupled plasma etching.

A highly doped silicon wafer is known to be brittle compared to its low-doped counterpart. Because the silicon crystals tend to form clumps during heating, they are more susceptible to breakage under certain conditions. Thermal expansion causes compressive stress, while weight transfer may result in cracks. In order to reduce these stresses, highly doped silicon wafers are fabricated at extremely high temperatures. These high temperatures produce a smooth surface.

When a semiconductor or electronic device needs to be highly doped, it is necessary to use a Highly Doped Silicon Wafer. A HDW is an excellent choice of material for many applications. It is able to resist 1x1019 electrons. The Heavily Doped Silicon Wafer has a boron dopant concentration of 1x1019 atoms/cm3. A thick HNA layer is also recommended for use in the electronics industry.

A Highly Doped Silicon Wafer can be classified into two types: N-type and P-type. The N-type is made from silicon. A highly doped silicon wafer is an N-type device. A high-doped silicon device is a semiconductor. This semiconductor is made by layering the silicon onto a substrate. The backside of the wafer is a polysilicon layer.

The Heavily Doped Silicon Wafer is different from its low-doped counterpart. A heavily doped silicon wafer contains a layer of silicon that is essentially a dislocation sink. It suppresses the diffusion of silicon self-interstitials into the epitaxial layer. This layer is located at the depth of 250 A from the substrate-epitaxial layer interface. A Heavily Doped Single Crystal Silicon Wafer is a very good example of a crystalline semiconductor.

A heavy doped silicon wafer contains dopants that make it a semiconductor. The typical N-type dopants include phosphorus, arsenic, and antimony. The P-type silicon wafer is a rare variety and is heavily doped with a low-level of boron. A heavy doped P-type silicon wafer has an extremely low resistance, about 1 Ohm.

The heavily doped silicon wafer is a densely doped material with 1x1019 atoms of boron per cm3. It is also a heavily doped semiconductor. The level of boron is at least 1019 atoms per cubic centimeter. This material has a high boron content. The oxygen content in the heavily doped silicon is uniform across the entire radius of the wafer and the toroidal core.

The heavily doped silicon wafer is a single crystal silicon. This material is characterized by a layer of dislocation loops at a depth of 250 A below the epitaxial layer. A heavy doped silicon wafer can also be called an N-doped wafer. Typically, the N-type dopants are used in the fabrication of vacuum tubes, desiccant tubes, gas detectors, and gyrostagens.

In addition to boron doping, the process also uses an HNA solution bath. During this process, a large amount of HNA is applied to the silicon wafers. The chemical solutions can also be channeled into a chemical cabinet through an input port 114. A chemical bath 110 collects used solution and periodically reapplies the semiconductor wafers. A fresh mixture of the chemical can sustain a high etch rate on the silicon substrate.

The Heavily Doped Silicon Wafer is a semiconductor device with an electrical resistivity of at least 100 mO/cm. The chemical solution is mixed with water and may be diluted with additional water depending on the application. The chemical solution may be sprayed onto the silicon wafers. If the chemical solution contains more than 100 mO/cm of silicon, the silicon wafer is heavily doped.

Why Use Highly-Doped Silicon Wafers?

In general, highly-doped silicon wafers are known to be more brittle than their low-doped counterparts. Since the silicon crystals tend to form clumps during heating, it is common for them to break easily under certain stress conditions. These stresses result from thermal expansion and compressive stresses due to weight transfer while using a transducer. The highly-doped silicon wafers are often fabricated by exposing them to high temperatures and pressure and then working them into a surface that is smooth and very similar to silica, which is used for many microelectronic applications.

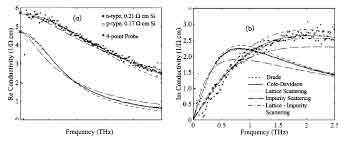

Recently, we've seen great advancements in the photo-electric microscopy field, where one exciting advance is the thermal conductivity of highly-doped silicon wafers. High-Performance Silicon (HPOS) has excellent thermal conductivity, which is due to the fact that the crystalline structure is tightly packed in the wafer structure. By creating an electrical field, we can actually send electric currents through the crystalline structure of HPOS. Not only is this method different from most other methods in the realm of photo-electric microscopy, but it also provides us with an opportunity to observe electron transfer between neighboring crystalline structures.

The highly-doped silicon carbide wafer was used for decades to create vacuum tubes, desiccant tubes, electrical insulators, desiccant tubes, gas detectors, gyrostagens, and thermal conductors. It was also used to make mechanical components such as bearings, valve seats, pawls, shaft seals, lock pins, hinges, bearing housings, cam locks, spring retainers, and knobs. Because of its versatile applications, this material was also used for electronic component fabrication.

When silicon carbide is used to make highly-doped silicon wafers, the temperature of the working chamber must be kept at approximately 300 degrees Celsius. This is to prevent the formation of bubbles during the scanning or electron micrographical processes. If the temperature is allowed to rise above this, the crystalline structure will collapse, thus, reducing the useful life of the highly-doped wafer. Another option to prevent the formation of bubbles during scanning is to have the temperature controlled using a vapor-gas control.

To produce highly-doped silicon wafers, it is first prepared by grinding the surface of the semiconductor. A fine mesh of aluminum oxide is then formed on the surface. Silicon carbide wafers are produced through the process of plasma cutting. After this, the fine aluminum oxide layer is sprayed with cure urethane, which prevents the crystalline structure from collapsing.

After this spraying, the wafer is then placed inside a spinning machine, where scanning electromagnetic energy passes through it. Depending on the thickness of the highly-doped wafer, the amount of radiation emitted is highly dependent on the scanning frequency. Once the energy flow passes through the highly-doped wafer, it creates a highly-radiant field that excites electrons in the wafer. These electrons travel through the device and ultimately enter the silicon layer on the surface of the wafer. Once there, they excitedly jump to an adjacent flat wafer surface, generating heat which hardens the wafer.

This hardening property is essential to the manufacture of highly-doped silicon wafers. The heat generated during this process hardens the wafer enough to be able to use it for future applications. It makes possible the creation of wafer sheets that have much better electronic properties than ordinary sheets of solid silica. With this ability, highly-doped sheets offer a higher bandwidth of data transmission and greater power efficiency.

[0]: https://cleanroom.byu.edu/ew_wafer_specs

[1]: https://www.nature.com/articles/s41598-019-46986-z

[2]: https://www.google.com/patents/US20110250739

[3]: https://www.ncbi.nlm.nih.gov/pmc/articles/PMC5853709/

[4]: https://iopscience.iop.org/article/10.1149/2.0081901jss

[5]: https://www.universitywafer.com/n-type-silicon.html

[7]: https://aip.scitation.org/doi/full/10.1063/1.5142889

[8]: https://en.wikipedia.org/wiki/Doping_(semiconductor)

[10]: https://nanoscalereslett.springeropen.com/articles/10.1186/s11671-021-03524-z